新型CMOS架構設計打破2D材料極限

編譯/高晟鈞

隨著矽基半導體即將到達其物理極限,縮小積體電路與電子元件的尺寸優勢在必行,找到替代的半導體材料將成為關鍵。

二維材料的好與壞

二維材料由於其穩定結構、優異的磁場效應特性與對短通道效應的免疫力(金屬氧化物達奈米維度時所出現的負面效應)而備受關注。儘管擁有許多優秀的特性,但當其套用在傳統矽基電路設計(CMOS和NMOS)時,卻由於極性控制技術有限而無法有效抑制快速上升的靜電功率而受到限制。

更多新聞: 取代矽基半導體 氮化物鐵電體改變電機領域遊戲規則

替代的「偽」CMOS架構

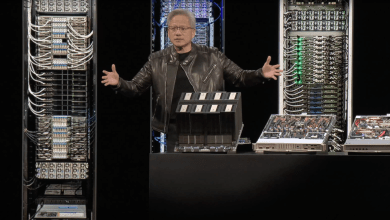

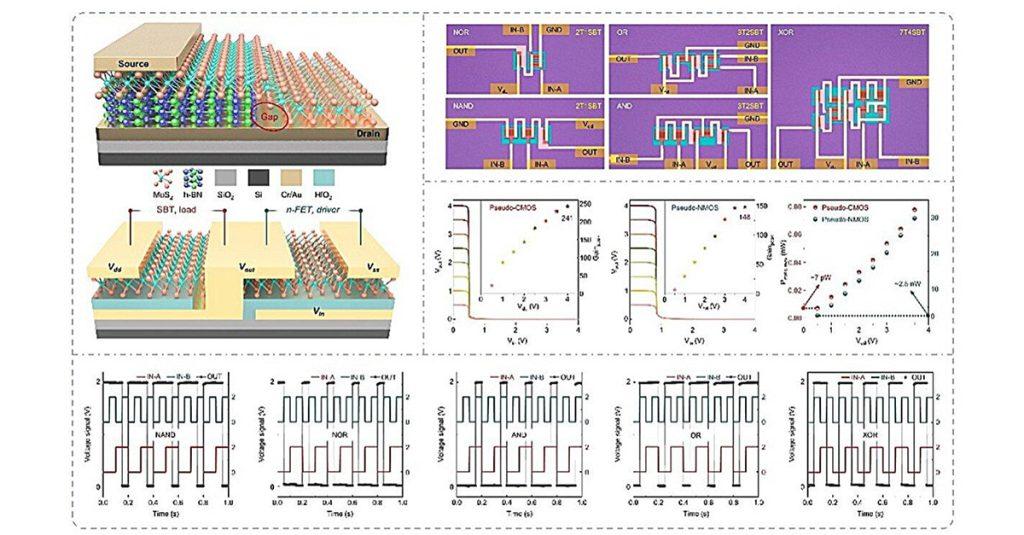

北京科技大學的研究人員近日推出了一種基於自偏壓(Self-biased)二硫化鉬電晶體的新型偽CMOS架構,專為2D材料進行超低功耗邏輯運算開發,希望替未來積體電路開發提供新的思路。

這種架構是透過串聯自偏壓電晶體(Self-biased transistors)作為負載開關,以n型場效電晶體 (n-FET) 作為驅動器來實現,其靜態功耗僅為同類裝置的1%和0.3%左右(分別為CMOS和NMOS元件)。

透過結合傳輸電晶體邏輯(PTL)設計,研究人員引入的新架構與傳統 IC 架構相比,電路中電晶體的數量減少了 80%,與先前推出的基於 CMOS 和 NMOS 2D 材料的電子產品相比,該團隊的架構規避了電晶體的極性控制,大大降低了其靜態功耗。

這項研究不只解決了二維材料在傳統積體電路上的難題,也為往後大規模開發各種複雜組合與時序電路奠定了良好的基礎。

資料來源:TechXplore

瀏覽 642 次