台積電公布1 奈米製程、1000億電晶體晶片路線圖

編譯/莊閔棻

近日,在美國舊金山舉行的國際電子裝置會議 (IEDM)上,台灣半導體巨頭台積電公布了自家半導體和下一代製程節點的產品路線圖。 在計畫中,該公司列出提供多個 3D 堆疊小晶片設計的目標,包括在單個晶片封裝中包含至少1000億個電晶體,以及最終推出1奈米製程的計畫。

台積電的路線圖

據外媒報導,在路線圖中,台積電談到要如何在 2030 年之前使用 1奈米晶片光刻技術製造晶體管的計畫,但這將以嚴格的生產速度進行,預計將於 2025 年底開始生產。而到 2028 年,該公司將轉向 1.4奈米的 A14製程,最終達到傳說中的1 奈米目標。目前,台積電將繼續開發2奈米的N2和N2P節點。

更多新聞:英特爾超車?執行長稱18A節點效能和發布時間將領先台積電N2

1000、2000億個電晶體的1奈米處理器

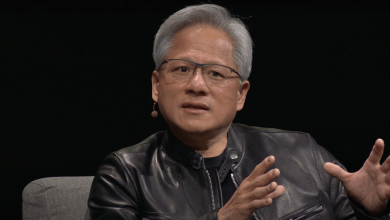

台積電預計自家的封裝技術,包括CoWoS、InFO、SoIC 等,都將在這幾年取得進步,並能在 2030 年建造初能建造超過1,000億個電晶體的大規模解決方案。台積電表示,雖然多晶片設計趨勢將持續下去,但幾年後,我們將看到由超過1,000億個電晶體組成的獨立解決方案。 同時,處理器也將繼續變得複雜,並出現擁有多達 2,000億個電晶體的處理器。目前,輝達(Nvidia) 擁有 800 億個電晶體的 GH100 是市場上最複雜的處理器之一。

讓英特爾「望塵莫及」

台積電執行長魏哲家在財報電話會議上表示,該公司有信心自家的製程節點將讓英特爾「望塵莫及」。台積電甚至還表示,他們已經「確認」增強的N3P 技術及3奈米級製造節點的效能將遠遠優於英特爾的18A 節點。

英特爾的反擊

不過,英特爾執行長Pat Gelsinger對這一說法似乎感到有些生氣,並反駁說,英特爾的18A工藝節點將優於台積電的2奈米晶片光刻技術。Gelsinger表示,英特爾的背面電力傳輸技術贏得廣泛讚譽,被認為在競爭中領先數年,非常強大。這項技術不但為矽提供更佳的面積效率、帶來更低的成本,同時還提供卓越的電力傳輸能力,進一步提高裝置整體性能。這將使英特爾在市場上擁有競爭優勢,領先台積電的下一代製程技術 N2。

參考資料:lowyat、wccftech、Tom’s Hardware

瀏覽 831 次