挑戰老大哥!聯電得手高通封裝大單 定新合作協議力抗台積電

編譯/莊閔棻

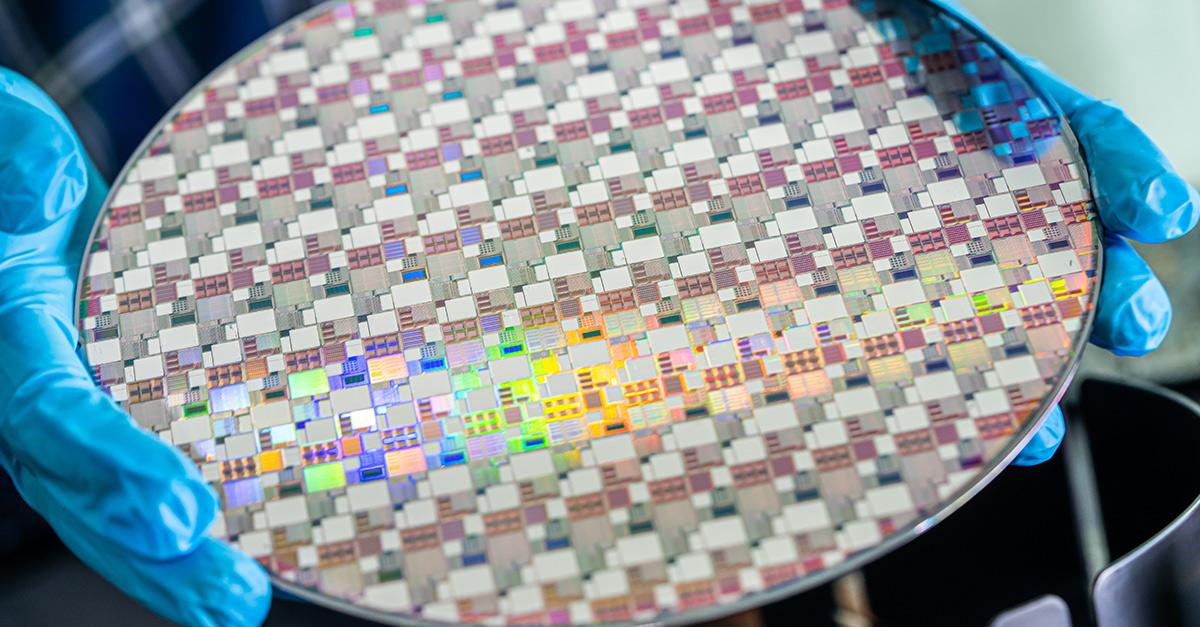

美國無線電通訊技術研發公司高通(Qualcomm)近日宣布與聯電(UMC)達成一項合作協議,計畫在未來的晶片中採用聯電的先進封裝技術,業界認為,這是高通在封裝技術上開始擺脫對台積電的高度依賴的關鍵一步,可能為晶片產業帶來新的競爭格局。

引發晶片產業競爭新局面

據報導,業內專家指出,高通的這項合作可能引發連鎖效應,吸引其他晶片設計公司效仿,進而對台積電的封裝技術市場構成壓力,隨著聯電技術實力提升,晶片封裝市場或將迎來更多競爭者,進一步改變產業生態。

更多新聞:台積電公開N2製程細節!如何為2031年GPU發展鋪路?

根據業界消息,高通計畫引入聯電的WoW Hybrid bonding技術,象徵聯電正式進軍先進封裝市場。分析指出,此次高通將採用聯電的晶圓堆疊技術,並結合PoP封裝工藝,取代以往依賴錫球焊接的傳統方式,這種設計大幅縮短了晶片間的訊號傳輸距離,無需依賴更先進的製程即可顯著提升晶片的運算效能。

聯電技術崛起成高通新選擇

長期以來,台積電不僅在晶片製造上保持領先,其CoWoS封裝技術也備受高通等大廠信賴。然而,隨著聯電在封裝技術上的快速進步,並達到接近台積電的性能水準,高通決定與聯電展開合作,成為首家嘗試突破台積電封裝領域壟斷的主要企業。

價格與供應穩定成合作關鍵

據悉,高通選擇聯電的主要原因包括價格競爭力與供應穩定性。由於台積電的先進技術需求過於集中,供應緊張成為高通的一大挑戰,相較之下,聯電不僅技術日益成熟,且能提供穩定且具吸引力的合作條件,為高通的產品策略提供更大的靈活性。

台積電地位仍穩固難以撼動

但儘管如此,高通並未完全放棄台積電的技術與服務,仍將旗艦系統單晶片(SoC)的製造工作交由台積電負責,顯示其在先進製程領域的地位依然穩固。同時,高通計畫於2025年進行聯電封裝技術的試產,2026年才會正式進入量產階段,代表台積電的封裝技術在未來幾年內仍將佔據重要地位,但市場競爭將逐步升溫。

高通與聯電的新合作標誌著晶片產業供應鏈的微妙變化,也為聯電開拓高階市場提供了重要機會。面對挑戰,台積電能否進一步鞏固其領導地位,將成為未來產業關注的焦點。

參考資料:Android Headlines

※探索職場,透視薪資行情,請參考【科技類-職缺百科】幫助你找到最適合的舞台!

瀏覽 1,966 次