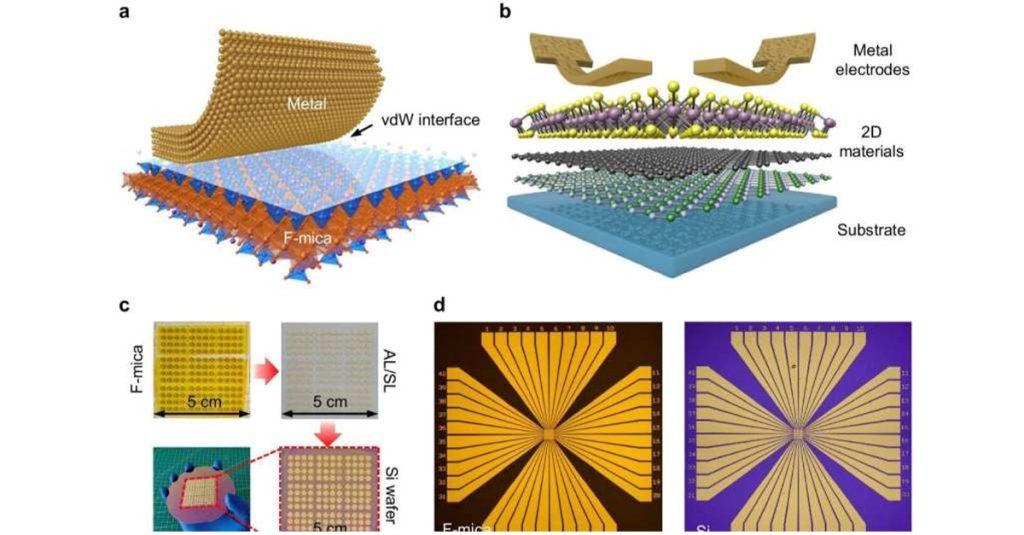

「凡德瓦力」介面 全堆疊技術突破製程障礙

編譯/高晟鈞

一研究團隊開發了一種創新的全堆疊技術,用於製造二維電子裝置,在優化二維材料與金屬電極間的介面接觸取得了重大進展。

突破製程障礙

在傳統二維電子裝置的製造流程中,金屬電極的沉積可謂是最為關鍵的一個步驟。然而,沉積在二維材料表面的高能量金屬原子容易破壞材料晶格,最終使得裝置的電氣效能不盡理想。因此,如何提高二維材料與金屬電極之間的介面的穩定性,對於提高二維電子裝置的性能至關重要。

更多新聞: 冷卻系統革命 解決縮小電晶體號的過熱問題

最近的一些研究表明,實現二維材料與金屬電極間的凡德瓦力接觸,可以避免眾多材料缺陷的產生,實現良好的介面電接觸,提高穩定性與大規模應用的潛力。

全堆疊技術

為了在材料與金屬電極間,實現穩定且可靠的凡德瓦力接觸,該團隊開發了一種全堆疊技術(All-stacking technique),避免了金屬沉積的步驟,並直接將金屬電極「堆疊」到二維材料上,進而保護材料受損,同時保留優異的電氣性能。

使用該技術製造的二維電子裝置,其金屬與材料接觸面具有光滑、清晰的凡德瓦間隙,且材料的側邊並沒有金屬原紫的摻雜。這表明了金屬電極與二維半導體間透過凡德瓦力成功結合,形成了穩定、高品質的介面。

技術潛力

使用全堆疊技術進行優化後的電晶體,其斷態電流(關閉狀態時的漏電流)降低了95%以上,次臨界擺幅(Subthreshold Swing)降低了50%。同時,它們還具又更高的開關比,使它們對於低功耗集成電路更有優勢。

為了展示全堆疊技術在晶圓級製程中的潛力,該團隊使用該技術製造了一系列基於單層二硫化鉬的場效電晶體陣列,其裝置良率高達98.4%,表現出優異的一致性與穩定性。

為了展示全堆疊技術在晶圓級製造中的潛力,該團隊使用該技術製造了一系列基於單層二硫化鉬的場效電晶體陣列。裝置良率高達98.4%,表現出優異的一致性與穩定性。

資料來源:TechXplore

瀏覽 814 次