全球首顆2奈米伺服器晶片亮相!AMD與台積電聯手推「Venice」

記者鄧天心/綜合報導

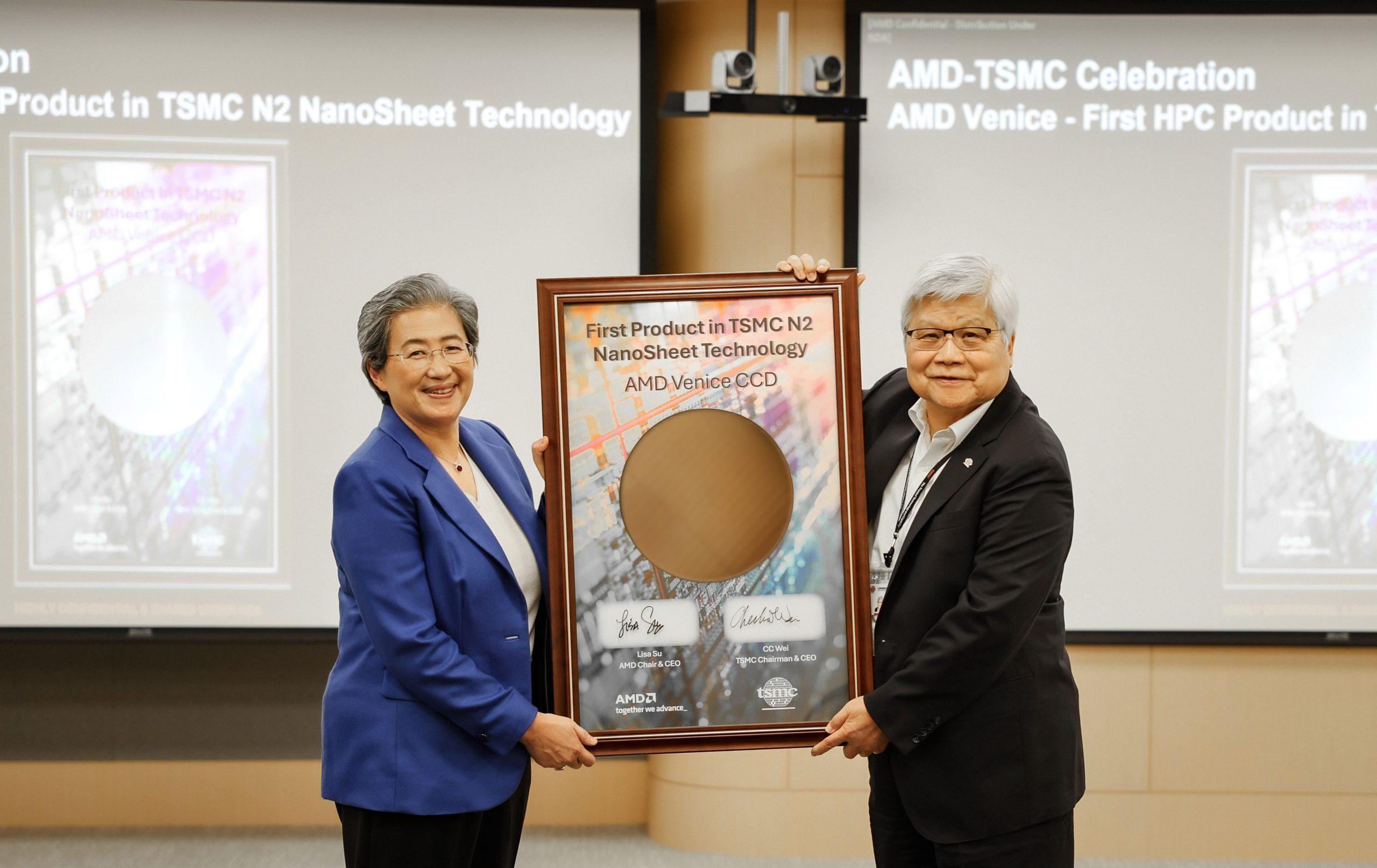

美國時間14日超微(AMD)宣布他們的新晶片「Venice」設計完成,準備開始製造,這顆晶片同時也是全世界第一顆用上台積電最新2奈米技術的伺服器晶片。Venice使用的是AMD最新一代的Zen 6架構,搭配台積電先進製程2奈米製程,把晶片的線路做得更細、更密,速度變快,也更省電,根據台積電的說法,這一代的晶片可以讓耗電量最多減少三分之一。Venice處理器預計將於2026年如期上市,AMD除了公布新一代處理器的進展,也同步宣布,第五代EPYC伺服器晶片已在台積電美國亞利桑那州的晶圓21廠完成驗證,並開始進入生產階段。

更多新聞:應對關稅衝擊 桃市電子業產業工會3訴求籲政府護勞工權益

台積電與AMD深化合作 啟動2奈米新時代

AMD董事長暨執行長蘇姿丰博士表示:「台積電多年來一直是我們的重要夥伴,透過與他們的研發與製造團隊密切合作,AMD得以持續推出在高效能運算領域具領導地位的產品,並不斷突破技術極限。」台積電董事長暨總裁魏哲家博士則指出:「我們很自豪能有AMD作為我們先進2奈米製程技術與亞利桑那州晶圓廠的領先HPC客戶,雙方的合作推動了關鍵技術的擴展,為高效能晶片帶來更出色的效能、更佳的能源效率與更高的良率。」

3D封裝進軍AI與雲端 運算速度大升級

AMD這次推出的Venice處理器,用了台積電最新的2奈米製程,還搭配兩種關鍵封裝技術:CoWoS-L和SoIC,讓整顆晶片不只更快,也更省電,CoWoS-L這項技術就像是把不同功能的晶片「拼圖式」地貼在同一塊底板上,中間用一種叫做「矽中介層」的材料連接,傳輸資料的速度會變快、距離也變短,這種技術甚至可以讓晶片支援多達12顆高頻寬記憶體(HBM),適合用在AI訓練或大型資料中心裡,處理大量資料;SoIC是一種3D堆疊技術,意思是晶片不再只是平放,而是像積木一樣往上堆,把不同功能的晶片疊在一起,可以縮短晶片之間的連線距離,反應速度更快、耗電也更低,特別適合用在需要高效能又節能的AI應用或雲端服務中。

不只技術上有突破,這顆Venice晶片的製造地點也很有指標性,是在台積電美國亞利桑那州的新廠Fab 21完成投片(設計送進工廠製造的第一步),並準備進入量產,AMD與台積電的深度合作,特別是在2奈米製程和先進封裝技術上的協同,將為未來的AI、雲端服務和高效能運算需求帶來更強大的支援。

蘇姿丰再訪台灣 分享AI時代的AMD轉型策略

今(15)日,AMD董事長暨執行長蘇姿丰博士再度來台,出席國立臺灣大學舉辦的椰林講座,以「AMD轉型AI領導者」為題發表專題演說,是繼去年6月於COMPUTEX以「高效能運算邁向AI時代」為題,發表開幕主題演講後,再度公開分享AMD面對AI時代的發展方向,她在講座中談到,AMD正透過CPU與GPU的雙主軸設計策略,結合開放式軟體生態系統,加速AI產品線的推進,同時也強調臺灣在全球半導體供應鏈中的關鍵地位,未來將持續深化與台積電等夥伴的合作。這場演講僅開放臺大師生參與,現場並安排問答與互動,顯示蘇姿丰不只看重技術落地,也積極與下一代科技人才交流,呼應AMD走向產業領導者的轉型之路。

瀏覽 626 次