神盾與ASICLAND攜手發展小晶片技術 有望延續摩爾定律!

記者 鄧天心/綜合報導

IC 設計廠商神盾EgisTec 5日宣布,與國知名晶片設計公司愛偲科技(ASICLAND)簽署戰略合作協議,將聯手開發人工智慧(AI)伺服器的小晶片設計,進軍高階數據中心市場,開拓韓國市場。

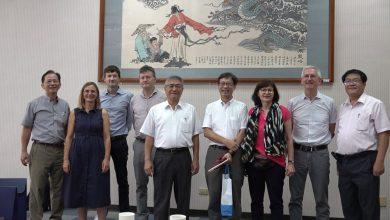

在合作夥伴台積電及安謀(Arm)代表的見證下,神盾董事長羅森洲與ASICLAND執行長李鍾民(James Lee)完成簽約。

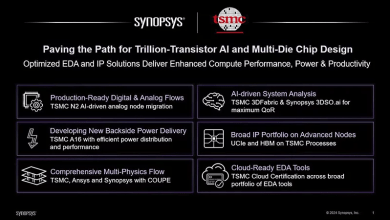

雙方首要合作重點將會是開發輸出輸入晶片(IO Die),其中將運用神盾的UCIe、LPDDR5等IP技術、ASICLAND的特殊應用晶片(ASIC)設計能力,以及台積電7奈米製程技術,再搭配安謀的CoWoS先進封裝技術,打造出理想的IO小晶片(Chiplet)解決方案。

這項技術將優先於韓國市場中推出,目前雙方已獲得第一筆訂單,未來計劃擴展至國際市場。

神盾與ASICLAND攜手強化AI HPC小晶片布局

羅森洲強調,神盾擁有CoWoS、UCIe和LPDDR5等IP優勢,可滿足客戶的客製化需求,節省製程成本並提供更具彈性的產品設計方案,同時也是全球半導體巨頭Arm的重要合作夥伴,自9月加入Arm Total Design計劃後,積極推動AI HPC Server產品,並採用台積電的先進製程技術。

另外,ASICLAND也在今天舉行台灣研發中心的啟用儀式,研發中心位於高鐵新竹站附近,將專注於3奈米、5奈米及CoWoS技術的研發。

羅森洲也提到,ASICLAND自2016年創立以來,一直是台積電在韓國唯一的價值鏈聯盟(VCA)合作夥伴,並與Arm維持全面設計(Total Design)夥伴關係。

Chiplet技術有望延續摩爾定律

Chiplet技術是一種透過先進封裝整合多個小晶片形成系統級封裝(SiP)的方法。在摩爾定律進入極限的背景下,Chiplet被認為是現在延續摩爾定律的方法。

傳統的微縮製程成本與技術挑戰日益增加,而Chiplet藉由將功能模組分割成多個小晶片,每個晶片的製造面積相對較小,因而能夠提高生產良率。

不同於傳統的單一大晶片設計,Chiplet能將各種功能的小晶片放在同一基板上,還可以將不同特性的晶片,如CPU、GPU、I/O晶片等分別製造,再透過先進封裝技術整合,

分析機構Omdia的數據顯示,Chiplet市場成長潛力可觀,預估2024年全球市場規模將達58億美元,並於2035年超過570億美元。

摩爾定律(Moore’s Law)是由英特爾(Intel)創辦人之一戈登·摩爾(Gordon Moore)於1965年提出的觀察,他當時觀察到,每隔約18到24個月,集成電路上可容納的晶體管數量將增加一倍,能使晶片性能提高、成本下降,摩爾定律因此成為了半導體產業的一個預測基準。

EUV(極紫外光刻)等技術雖然在一定程度上延續了摩爾定律,但成本高昂、技術複雜,因此,近年來,也有公司透過異質整合(如Chiplet技術)來提升晶片性能。

瀏覽 273 次