重大突破!台積電從圓形到矩形矽晶片的漫長道路

編譯/莊閔棻

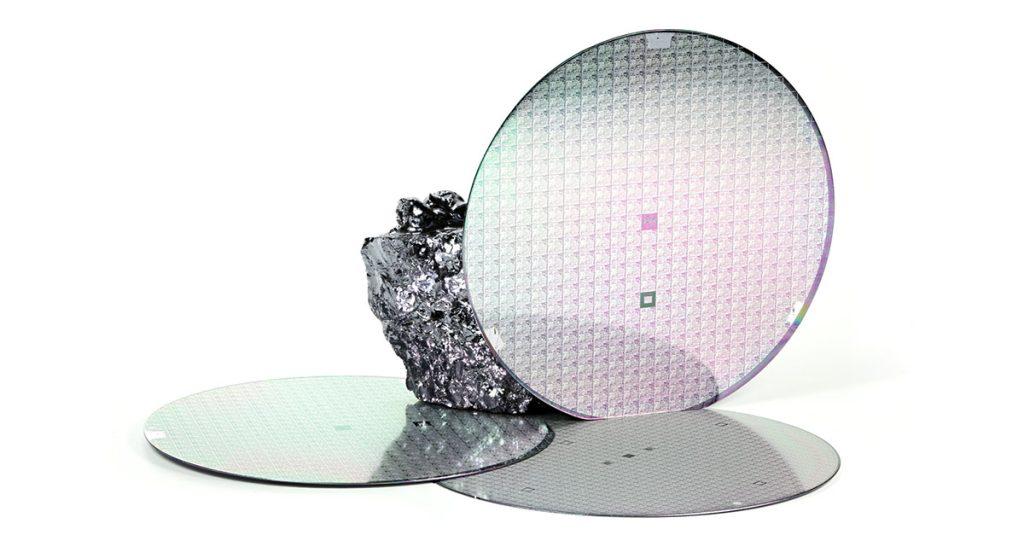

晶片製造巨頭台積電(TSMC)正在試驗一種矩形晶圓技術,可能會徹底改變晶片製造業。為取代目前標準的12吋(300毫米)圓形晶圓,台積電正在測試尺寸為510毫米 x 515毫米的矩形基板。

傳統晶圓的浪費

傳統的圓形晶圓由於其形狀問題,使相當數量的晶片模組被切割時產生浪費,特別是對於像輝達的H200這樣大型晶片(814平方毫米)來說,浪費的比例更加顯著,然而採用矩形晶圓後,每塊晶圓上可容納的晶片數量預計將增加三倍,允許每個晶圓生產更多晶片並減少邊緣浪費,大大提高生產效率和經濟效益。

更多新聞:台積電開始生產英特爾3 奈米製程CPU

CoWoS已不足

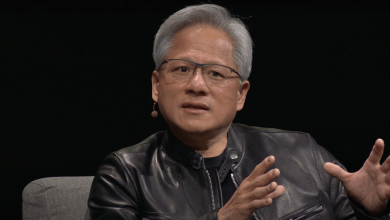

台積電表示,他們正「密切關注先進封裝的進展和發展,包括面板級封裝。」該公司目前的先進晶片封裝技術,如 CoWoS,使用的是 300 毫米矽晶圓,儘管這對於為輝達、超微半導體(AMD)、亞馬遜和Google等客戶生產 AI 處理器非常重要,但隨著AI晶片尺寸和複雜性的增加,這些方法的效率可能會下降,因此需要新的矩形基板。

「柴可拉斯基法」

大家可能不知道,晶圓之所以採用圓形,是因為目前的使用的「柴可拉斯基法」(Czochralski method)生產流程,此方法由波蘭科學家Jan Czochralski於1915年發明,生產出棒狀的矽晶體,然後切片成圓形晶圓。然而,將圓形晶圓改為矩形並非不可能,只是這需要更新整個生產流程和製造線,代表台積電將無法使用傳統的晶圓廠工具,傳台積電目前正在與設備和材料供應商,合作開發這種新的封裝技術,但沒有透露細節。

可能要五到十年

過渡到矩形基板在技術上具有挑戰性,被認為是長期計畫,可能需要五到十年的時間,儘管目前尚不清楚矩形晶圓技術何時會正式投入生產,但在當前激烈的市場競爭中,這項技術的巨大潛力無疑會推動其盡快實現量產,為晶片製造業帶來了新的希望,也預示著未來可能會出現更多的技術突破。

參考資料:hackaday、Tom’s Hardware

瀏覽 1,144 次